Firma AMD wypuściła wreszcie na rynek nową architekturę Barcelona. Pierwsze produkcyjne egzemplarze procesorów trafiły już do klientów. Barcelona jest pierwszym od dłuższego czasu jądrem, które wprowadza tak poważne zmiany do konstrukcji procesorów AMD. Ostatnia tego rodzaju rewolucja miała miejsce w momencie inauguracji architektury K8 i ukazania się na rynku pierwszych Opteronów i Athlonów 64. Poza usprawnieniami architekturalnymi, K10 - bo tak brzmi oficjalna nazwa kodowa Barcelony - może się również pochwalić obsługą nowych wersji technologii znanych już z K8.

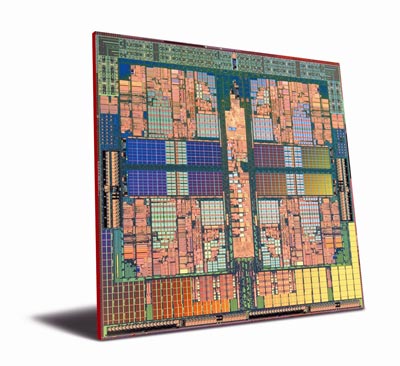

Barcelona jest pierwszym procesorem AMD wyposażonym w cztery rdzenie, przy czym warto zauważyć, iż w odróżenieniu od rozwiązań Intela, na Barcelonę składają się cztery niezależne jednostki. Intelowskie czterordzeniowe jądra Clovertown i Kentsfield oraz nadchodzące dopiero Harpertown i Yorkfield są tworzone z dwóch układów Core połączonych na jednej podkładce. Powstające w ten sposób konstrukcje mogą się również pochwalić czterema jądrami, jednak nie są to rozwiązania zaprojektowane od zera jako czterordzeniowe.

AMD wyposażyło architekturę Barcelona w szereg usprawnień. Składają się na nie, między innymi, ulepszony cache, nowy kontroler pamięci, nowe algorytmy przewidywania rozgałęzień i pre-odczytu pamięci, poprawione zarządzanie energią i pakiet rozszerzeń AMD-V.

Pamieć cache Barcelony jest o tyle interesująca, że zawiera również cache L3, które to rozwiązanie widzieliśmy ostatnio w zapomnianych już praktycznie procesorach K6-III+ i K6-2+. Cache trzeciego poziomu jest w przypadku K10 32-drożną pamięcią asocjacyjną, liczy sobie 2 MB i jest wspólny dla wszystkich rdzeni procesora. Dodatkowo każde z jąder ma do dyspozycji 512 KB 16-drożnego asocjacyjnego cache'u L2 i 128 KB 2-drożnej asocjacyjnej pamięci cache L1, dokładnie tyle samo, co w układach poprzedniej generacji.

Procesory oparte na architekturze K10 będą więc miały łącznie 4,5 MB pamięci podręcznej. Da porównania, Intelowskie czterordzeniowe Clovertown i Kentsfield dysponują 64 KB cache'u L1 na jądro, a każdy zestaw dwóch rdzeni ma też do dyspozycji 4 MB dzielonego cache'u L2. £ącznie daje to 8,25 MB.

AMD poprawiło również wydajność sterownika pamięci, który w przypadku Barcelony skonstruowany jest trochę inaczej niż w dotychczasowych procesorach. Zamiast jednej 128-bitowej szyny pamięci, AMD zastosowało dwa kontrolery 64-bitowe. W założeniu mają one pracować niezależnie od siebie, pozwalając uzyskać lepszą przepustowość.

Nowy kontroler pamięci został zaprojektowany z myślą o przyszłych technologiach. Premierowe egzemplarze Barcelony współpracują z pamięcią DDR2, ale już pierwsza przyszłościowa rewizja architektury, ochrzczona nazwą Shanghai, będzie oferowała wsparcie dla nowych kości

DDR3.

Nowością w sterowniku pamięci jest układ pre-odczytu pamięci DRAM, którego zadaniem jest pobieranie potencjalnie użytecznych danych i przetrzymywanie ich do wykorzystania w późniejszych operacjach. Prefetcher ten ma swój osobny bufor i nie zaśmieca żadnego z poziomów cennej pamięci cache.

Barcelona ma też nowy, 512-bitowy moduł przewidywania rozgałęzień podobny do tego, który Intel zastosował w swoich procesorach Pentium M. Zwiększona dzięki niemu wydajność układu przekłada się, między innymi, na mniejsze zużycie energii.

Kolejnym usprawnieniem Barcelony w stosunku do K8 jest poprawiony prefetcher pamięci cache. Choć nadal każdy z rdzeni procesora ma do dyspozycji dwa takie układy, są one wyposażone w poprawiony algorytm logiczny, co w praktyce pozwala osiągnąć lepszą wydajność. Co więcej, dzięki nowemu algorytmowi możliwe jest ładowanie danych przewidzianych jako potrzebne bezpośrednio do cache'u L1, podczas gdy układ pre-odczytu stosowany w architektucze K8 odkładał je w pamięci cache L2.

Również obsługa pełnych 128-bitowych instrukcji SSE jest sporym krokiem naprzód w porównaniu z K8, który mógł co najwyżej pochwalić się zdolnością wykonywania dwóch 64-bitowych instrukcji jednocześnie.

Efektem tego ograniczenia K8 było marnowanie czasu na podział każdej 128-bitowej instrukcji na dwa możliwe do wykonania 64-bitowe elementy. Barcelona nie ma tego problemu, a co za tym idzie, wykonuje instrukcje SSE szybciej od poprzednika.

Również prędkość odczytu instrukcji SSE poszła w górę - z 16 bajtów na cykl procesora w przypadku K8 do 32 bajtów na cykl w Barcelonie. Co więcej, AMD poprawiło także przepustowość wewnętrznego połączenia pomiędzy kontrolerem pamięci, a pamięcią cache L2 z 64 do 128 bitów na cykl procesora.

Kolejną pozycją na tej sprawiającej wrażenie, jakby się miała nigdy nie skończyć liście usprawnień, które AMD wprowadziło w swojej nowej architekturze, jest ważna zmiana w zarządzaniu energią. Otóż w Barcelonie jądro procesora i kontroler pamięci mają osobne zasilanie, dzięki czemu każdy z tych elementów może pracować z inną prędkością i na innym napięciu. Niestety, konfiguracja obecnych płyt głównych uniemożliwia wykorzystanie tej innowacji.

Na oszczędność energii przez Barcelonę ma też wpływ fakt, iż każde z jąder procesora może dostosowywać swoją prędkość taktowania do aktualnego obciążenia. Dzięki takiemu rozwiązaniu nowe układy powinny oddawać podobną ilość ciepła, co obecne dwurdzeniowe Opterony.

Na koniec warto wspomnieć o instrukcjach AMD-V, które oferują sprzętowe wsparcie dla techniki stronicowania znanej jako shadow paging. Umożliwia on systemom operacyjnym zainstalowanym na maszynach wirtualnych bezpośredni dostęp do pamięci. AMD nazywa tę nową funkcjonalność nested paging.

Wszystkie te usprawnienia architektury oraz posiadanie czterech rdzeni powodują, że Barcelona liczy sobie

463 miliony tranzystorów, co nie wypada szczególnie imponująco w porównaniu z procesorami Xeon Kentsfield Intela, które mimo prawie dwukrotnie większej pamięci cache, mają raptem 582 miliony tranzystorów. Jest to o tyle martwiące, że podobnie jak „stare” Xeony, układy z serii Barcelona będą produkowane w technologii 65 nm.

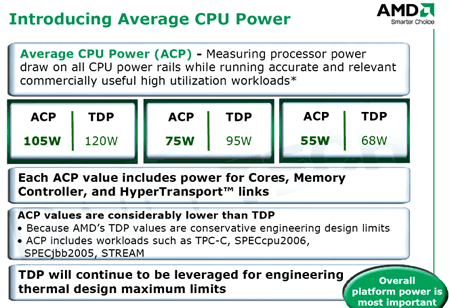

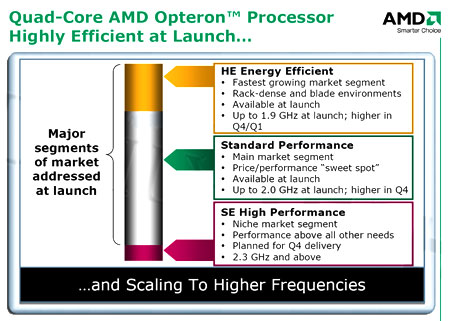

Czterordzeniowe K10 zużywają tyle samo energii, co dostępne obecnie dwurdzeniowce. Identyczna z obecną jest również polityka AMD w kwestii ciepła oddawanego przez nowe procesory, na skutek czego Barcelona pojawi się w trzech wersjach różniących się współczynnikiem TDP. Poza standardowymi układami dostępne będą również chłodne, lecz mniej wydajne HE, oraz bardziej grzejące się, lecz wysokowydajne SE. Modele SE pojawią się jednak dopiero w ostatnim kwartale 2007 roku.

AMD wyznaczyło też dla każdej z wersji Barcelony nowy rodzaj współczynnika - ACP, który wyraża całkowity pobór mocy przez jądro procesora, kontroler pamięci i złącze HyperTransport. Pomiarów dokonano po obciążeniu układów „zadaniami realistycznymi z punktu widzenia użytkownika dostępnych na rynku programów”.

Aplikacje, które wykorzystano do pomiaru ACP, to między innymi TPC-C, SPECcpu2006, SPECjbb2006 oraz STREAM. Współczynnik ACP jest zasadniczo niższy od TDP, lecz zdaniem AMD dużo lepiej odzwierciedla poziom ciepła oddawanego podczas rzeczywistej pracy, podczas gdy TDP jest dla bezpieczeństwa sztucznie zawyżany.

AMD przygotowało na premierę Barcelony dziewięć modeli Opteronów z serii 2300 i 8300. Ich prędkości taktowania oscylują pomiędzy 1,7 a 2,0 GHz, aczkolwiek szybsze wersje zostały już zapowiedziane na ostatni kwartał 2007. AMD ma też nadzieję wypuścić na rynek procesory taktowane od 2,3 GHz wzwyż dzięki modelom SE. Ich współczynnik TDP będzie jednak wynosił 120 W.

Premiera opartych na architekturze Barcelona Opteronów 2300 i 8300 ma się odbyć dzisiaj (10 września). Posiadacze płyt głównych wyposażonych w podstawki Socket AM2, którzy chcieliby zaopatrzyć się w czterordzeniowy procesor, będą musieli jeszcze trochę poczekać na jedno-socketowe Opterony z jądrem Budapest bądź oparte na jądrze Agena Phenomy X4 i FX.

Pierwsze testy Barcelony można znaleźć na stronach:

Komentarze

0Nie dodano jeszcze komentarzy. Bądź pierwszy!